# CT25205

## IEEE 802.3cg® IOBASE-TIS Digital Controller

## **Status**

- Silicon-Proven

- Fully characterized

- EMI tested (in combination w/ CT25203)

- In mass production

## Deliverables

- RTL Object-Code

- Integration-level Verification Env. (UVM)

- Protocol Compliance & Coverage Report

- SDC Constraints

- Integration Guide

## **Applications**

- Automotive Networks

- Industrial Networks

### CT25205 MII TX PCS-TX PMA-TX MII CRS MII\_COL COLLISION DETECTOR MII-RX PMA-RX CLOCK ENHANCED NOISE IMMUNITY MNGR CLK 100M CT25205 STANDARD REGISTERS

## **Features**

- Compliant to:

- IEEE 802.3cg® specifications

- OPEN Alliance TC14 PMD Transceiver INTERFACE

- OPEN Alliance TC10 Sleep Wake Up

- OPEN Alliance TC14 PLCA Diag.

- OPEN Alliance TC14 Interoperability Specifications

- OPEN Alliance TC14 EMC Specifications

- OPEN Alliance TC14 System Implementation

- Compatibility with any Clause 4 compliant MAC

- Optimized for very low latency and low TO TIMER

- Enhanced Noise Immunity PMA operation (ENI)

- TX/RX SFD detection

- False Carrier signaling over MII

- Collision detection masking

- PCS and PMA loopback mode

- PCS remote jabber detection

- PCS reflection mode

- PLCA Precedence Mode

- PLCA RX FIFO Mode

- PLCA leader (coordinator) selection

- Configurable PLCA Burst Mode

- Optional MDIO Clause 22 slave module

- Optional PLCA BEACON/COMMIT extensions over MII

- Optional PCS "Unjab" timer support

## **Description**

The CT25205 Digital IP core provides the PMA, PCS, and PLCA Reconciliation Sublayer building blocks of a standard IEEE 802.3cg® 10BASE-T1S Ethernet Physical Layer.

The RTL code is written in plain Verilog 2005 HDL, and it is fully synthesizable on standard cells and FPGA systems. It works in conjunction with any standard IEEE CSMA/CD Clause 4 Ethernet MAC using MII.

The integrated PLCA RS allows existing MAC devices that do not support the new PLCA MII extensions to take advantage of the PLCA advanced features. On the other end, the PMA connects to a standard OPEN Alliance 10BASE-T1S PMD Interface.

The CT25205 can be used in conjunction to other analog and digital blocks like (a) the CT25203 to implement a complete physical layer ethernet device, (b) the CT25208 to implement a digital MACPHY and (c) the CT25203, the CT25208 and the CT25209 to implement a complete OPEN Alliance MACPHY (see next page for details).

# **IOBASE-TIS IPs**

## Frequently-Asked Questions

#### Q: Which kind of IC products I can develop using Canova Tech 10BASE-T1S silicon IPs solution?

A: Among others, here're some product examples you can develop with our 10BASE-T1S silicon IPs:

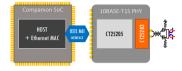

OPEN Alliance 10BASE-T1S PMD Interface IC + Companion SoC/FPGA

OPEN Alliance 10BASE-T1S MACPHY + Companion low-end MCU/FPGA Sensor with integrated 10BASE-T1S interface 10BASE-T1S IEEE PHY + Companion Ethernet SoC

This 2-chip 10BASE-T1S networking solution mimics the CAN partition.

The CT25203 Analog Front-End plus the CT25207 PMD Controller are integrated, using BCD silicon technology process, in a single low pin-count tiny and low-cost chip. By means of the standardized OPEN Alliance three-pin PMD Interface, it then connects to the SoC which integrates the Host, the CT25208 Ethernet MAC, if needed, and the CT25205 digital PHY in a pure digital silicon technology.

This innovative 2-chip 10BASE-T1S networking solution is based on the standardized <u>OPEN Alliance SPI</u> MACPHY Interface.

A single low pin-count, tiny "MACPHY" chip, made using BCD silicon technology process, integrates the CT25203 Analog Front-End, the CT25205 digital PHY, the CT25208 Ethernet MAC and the CT25209 SPI Protocol Handler. A low-end companion SoC/FPGA, is then connected to the MACPHY via a standard SPI interface.

Automotive and Industrial sensors often integrate LIN and/or CAN interface in a single chip solution using BCD silicon technology.

The substitution of LIN and/or CAN interfaces with 10BASE-T1S Ethernet can be then realized by means of the CT25203 Analog Front-End, the CT25205 digital PHY and the CT25208 Ethernet MAC directly connected to the Host Sensor in a similar way of LIN and/or CAN.

This is the "classical" Ethernet networking solution.

A standard 10BASE-T1S PHY integrates the CT25203 Analog Front-End plus the CT25205 digital PHY in a BCD silicon technology connecting, via the IEEE standard MII/MDIO Interface, to a companion Ethernet controller SoC. The world-first 10BASE-T1S PHY, in form of Test Chip vehicle and based upon the CT25203 and the CT25205, has been released by Canova Tech in 2018. Have a look here for details.

#### Q: Are there any way to test the Canova Tech 10BASE-T1S silicon IPs solution?

A: Yes, by subscribing the "Early Access" program you can receive our development boards described <u>here</u> and the related technical support. Contact us for commercial details.

#### Q: Why the 10BASE-T1S front-end requires to be implemented on BCD technologies?

A: Because of the nature of the multi-drop network which obliges the silicon interface to expose high value of impedance to the line. In fact, in presence of severe electromagnetic radiations induced on the twisted-pair, the line common-mode voltage can then reach the silicon with high-voltage peaks of  $\pm$  tens of Volts. The BCD process ensure proper protection of the silicon against damages and avoid degradations of the quality of the communication in those severe conditions.

Contact us for checking if your target silicon process can be used for implementing the 10BASE-T1S front-end.

#### Q: May I ask Canova Tech to develop custom and dedicated analog and/or digital on top of the IPs?

A: Yes, you can. Our business model includes custom and dedicated Design Services to facilitate the integration of our IPs into your chip architecture. This business model includes the possibility for you to assign Canova the responsibility for design of a complete integrated circuit (GDS IP) based upon our IPs and your requirements.

### Q: Is 10BASE-T1S protected by Standard-Essential Patents (like for CAN, 100BASE-T1, etc.)?

A: Yes, it is. the Physical-Layer Collision Avoidance Reconciliation sub-layer (clause 148 of the IEEE 802.3cg® standard) has been invented and patented by Canova Tech. We're always available to license it to you on the basis of FRAND (Fair, Reasonable and Non-Discriminatory) conditions already applied to several active licensee of Canova Tech's Intellectual Property Rights.

Contact us for setting the required NDA and receive the PLCA Patent Agreement.

#### Q: Which options do I have for licensing the Canova Tech 10BASE-T1S silicon IPs solution?

A: You can have several licensing options which includes:

- <u>single-use/multiple-use license</u>: the IPs (single or in bundle) are delivered as object-code and licensed for the use on a well-defined product code (single-use) or for unlimited product codes (multiple-use).

- <u>architectural license</u>: the IPs (single or in bundle) are delivered as source-code (plus know-how transfer) and licensed for the use on unlimited product codes.

- manufacturing license: here Canova Tech can develop your entire product, based upon our IPs (single or in bundle) and your product specifications. The GDS IP is licensed and delivered to you (including all necessary documentation and support) for you to manufacture your product and brand it.

### Q: What kind of Support and IP Maintenance will I get from Canova?

**A:** You will get all required Support and IP Maintenance to ensure proper IP integration into your products for 12 months following the IP licensing. You can then subscribe, at your option, annual renewals of the Support and Maintenance agreement.